前言

这篇文章关于VLSI Testing,内容不是特别多也不是特别详细,主要就是有些概念之类的知道就好,后面的DFT部分感兴趣可以继续研究一下,内容十分多。想要看安全部分的师傅可以等下一篇,下一篇是 Scan-Based Side-Channel Attack。

VLSI Testing

为什么要介绍VLSI Testing:加密芯片的测试基础设施可以成为泄露芯片秘密信息的后门

基本内容

逻辑是否有误,电路故障

首先是VLSI从需求到问世的生产过程

用户需求-选择需求-计划-设计验证-测试开发-生产-生产测试-面向市场

然后是设计过程

概念-设计-功能实现 设计验证过程

功能实现-功能集成-电阻晶体管设计 电阻晶体管逻辑验证 wafer

电阻晶体管设计-逻辑集成-逻辑门与逻辑网络 逻辑验证 chip

逻辑门与逻辑网络-整体布局-实现布局 布局验证 PCB

实现布局-生产-产品 产品测试 Sytem

其中有一个十倍理论:每一个过程比上一个过程需要的维修替换成本高出十倍,在当今更是远远超过十倍。所以生产过程的测试是为了以最少的成本保证高质量高可靠性。

Defect, Yield and Defect Level

Defect从不同层次上看可以称作缺陷,错误和故障。缺陷是硬件层次存在问题。错误是输出信号错误,故障是功能故障

其中功能故障存在多种情况:信号滞留故障,信号桥接故障,延迟故障,卡开卡短故障。

Yield是在生产过程中没有缺陷的芯片比例。计算方式是每单位区域的芯片平均缺陷数乘以芯片区域大小乘以测试区域除以故障参数加1取负的故障参数次幂。

Defect level是表示每百万件芯片有多少件有缺陷。计算方式有两种:一种是记录生产的芯片有缺陷的个数,根据总的芯片数量归一化为每百万。另一种是根据良率计算,公式为当前测试区域的良率减去当测量区域为1时的良率除以当前区域良率。

最基本的思路:预设结果和实际结果异或操作

功能测试:通过验证回显和预设正常的模板判断是否存在缺陷。随着电子电路的功能增加,需要验证的输入输出也增加,所以功能测试变得不再适宜。

结构测试:根据逻辑门类型,连接情况,网络结构简化功能测试进行测试。

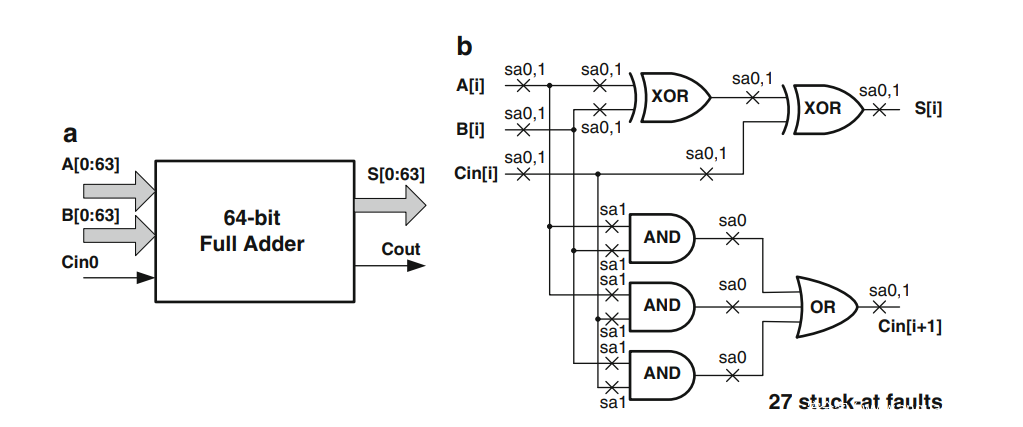

根据功能测试,我们要验证ABC的输入和S和cout的输出,也就是129个输入65个输出,也就有2 ^129和2 ^65情况,显然是一个巨大的工作量。

如果使用结构测试,对于每一位的01存在18个节点,36个状态,再根据逻辑门性质(and有0出0,or有1出1),36种状态中有9个状态只需要考虑1或者0的状态。所以只需要27个状态,再加上是64位,存在27*64种情况需要验证,显然比功能测试少。

可控程度是指控制输入为0/1的容易程度

可读程度是指通过输出判断节点信息的容易程度

DFT

在设计之初就添加额外的电路设计以实现测试的需求。

优点:提高故障覆盖率,减少测试模型生成的时间,减少测试时间,实现分支测试和并行测试,减少生产周期开销。

缺点:多余硬件成本,降低良率,降低性能,设计时间增加。

同时,由于DFT提供了观察和控制芯片存储模块的功能,芯片也变得不再安全。

首先我们介绍结构性测试

其中包括扫描,部分扫描,边界扫描

扫描是通过对全部触发器控制实现输入输出可控可观察

部分扫描是通过部分触发器控制实现输入输出可控可观察,相比于扫描降低了测试完整性提高了空间利用率和经济效益。

边界扫描通过链接主要输入和输出实现可控可观察。

对扫描的介绍主要是简化

由于扫描需要对全部触发器实现控制,在芯片越来越复杂的今天,这一工作量是巨大的,同时由于处理每一个触发器的时间无法无限缩短,所以我们需要通过增加链数减小链的最大长度来缩短总时间,但是链的最大长度的减小表示着测试覆盖率的降低(一条完整的链能够完全检测覆盖的逻辑与电路,将这条链一分为二,显然两条链连接部分的逻辑与电路失去了测试的覆盖)。所以我们要寻找新的方法在不降低覆盖率的同时,减少测试数据。

这里我们介绍基于LFSR的压缩,其他的方法可以自行学习。

首先我们要知道哪些部分是可以被压缩的。第一部分是don’t cares。在前面的学习中,我们已经知道don’t cares 是不影响输出的部分,也就是在测试过程中不需要控制和检测的部分。而一个电子电路中,don’t cares的数量是巨大的,只有1~5%的输入时需要考虑的。那么我们对don’t cares做什么处理呢,是固定设置还是随机设置呢。当随机设置时,会出现大量01变换,造成了功率的消耗,所以我们使用固定设置减少01变化。

接下来时LFSR压缩的基本思想: 通过种子实现测试模型。

种子如何生成。

我们记录01的转折点而不是那些care的输入。其中don’t cares 我们记作X

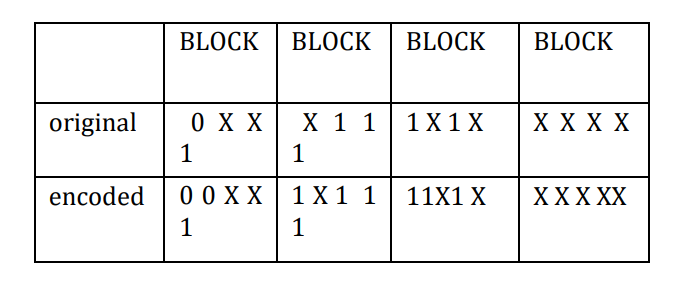

对于模块中存在转换或者当前模块没有转换但是和上一模块最后的care值存在转换,我们记录0作为标记,对于没有转换的模块标记1,对于模块中全是don’t cares的模块我们标记X。

当读取到标记1时,对于don’t care的部分我们输入与前面一致的01,当标记为0时,我们根据LFSR生成01,当是X标记时,可以采用前面任意一种方式。

例子

四个输入为一组的四个模块,

第一个模块有转换,记录0,其余数据抄回,第二个模块无转换,记录1,第三个模块同样,第四个模块为don’t cares 模块

在编码之前,存在7个care点

编码后,除了最后一个don’t cares 模块的标记不需要记录,前三个模块标记需要记录,除此之外,要记录转换模块中的转换位置即记录开头0位置以及开头1位置。也就是只需要关注5个点就够了。

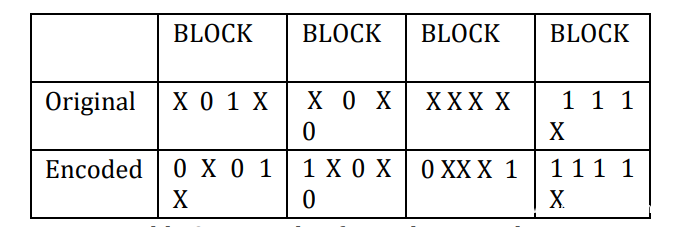

特殊的

第一个模块有转换0开头1结尾,第二个模块内部没有转换,但是第二个模块为0与前一模块1结尾出现了转换,所以记作转换。第三个模块为don’t cares模块,根据前后模块关系决定处理模式:在上面的例子中,前一模块结尾为0,后一个模块开头为1,所以我们将第三个模块当作转换模块处理,以1结尾。

进一步我们寻找可压缩点,对于原数据我们压缩01重复,对于压缩后的数据,我们压缩重复的标记

记录01X时,可能存在多个模块类型一致,也就不需要改变标记了。

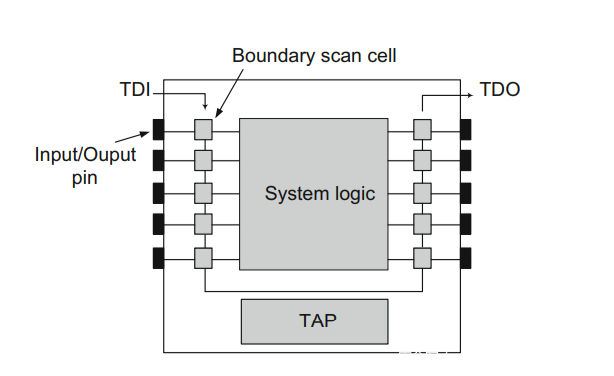

接下来是边界扫描,主要介绍工作原理

工作原理

边界扫描可以针对芯片,集成电路板,系统进行测试。其中最主要的是集成电路板的扫描。

移位寄存器的输入称为测试数据输入(TDI),而移位寄存器的输出称为测试数据输出(TDO)。TDI和TDO分别表示JTAG接口的输入和输出。有限状态机,称为测试访问端口(TAP)控制器,基于三个信号控制所有可能的边界扫描功能,这三个信号是外部时钟(TCK)信号,测试模式选择(TMS)信号,和可选的测试复位(TRST)信号

在测试模式下,芯片的输入/输出引脚与逻辑块的主输入/输出之间不再有直接连接。芯片的输入/输出引脚在测试模式下被重用为扫描引脚.这有效减少了引脚个数。

发表评论

您还未登录,请先登录。

登录